# Pengkodean Kanal Reed Solomon Berbasis FPGA Untuk Transmisi Citra Pada Satelit Nano

Ainun Jariyah, Suwadi, dan Gamantyo Hendrantoro Jurusan Teknik Elektro, Fakultas Teknologi Industri, Institut Teknologi Sepuluh Nopember (ITS) Jl. Arief Rahman Hakim, Surabaya 60111 E-mail: suwadi@ee.its.ac.id, gamantyo@ee.its.ac.id

Abstrak-Dalam sistem komunikasi dari satelit ke stasiun bumi terdapat beberapa blok penyusun agar sistem dapat berjalan dengan baik, dan salah satunya adalah blok pengkodean kanal di sisi satelit. Pada blok pengkodean kanal berisi metode penambahan simbol parity (codeword) ke dalam data saat proses pengiriman dengan tujuan meningkatkan kemampuan koreksi kesalahan data yang akan diterima. Jenis pengkodean kanal vang digunakan adalah Reed Solomon code (255,239) yang dirancang dengan menggunakan bahasa pemrograman VHDL melalui software Quartus II, dan diimplementasikan pada hardware FPGA menggunakan Altera DE1 board. Informasi yang ditransmisikan berupa data citra dengan format file JPEG. File citra yang terdapat di komputer dikirim secara serial dari console terminal emulator menuju FPGA yang berisi program encoder, sehingga di dalam FPGA inilah terjadi proses pengkodean data. Data citra yang dikirim adalah data berkapasitas 68,1 KB. Namun secara implementasi hasil pengkodean berupa penambahan codeword tidak dapat diamati langsung, melainkan hanya bisa diamati melalui simulasi. Namun akibat yang ditimbulkan dari penambahan codeword adalah perubahan warna yang terjadi pada citra yang telah dikodekan Hasil simulasi dari pengkodean Reed Solomon (255,239), berupa 16 byte codeword (16 simbol) yang disisipkan dibelakang urutan symbol informasi sebanyak 239 byte.

Kata Kunci-Reed Solomon (255,239), Citra, FPGA, VHDL

# I. PENDAHULUAN

APLIKASI sistem komunikasi satelit saat ini telah banyak dilakukan dan dikembangkan secara mandiri oleh beberapa perguruan tinggi maupun lembaga penelitian di Indonesia, dan salah satunya adalah perguruan tinggi yang yang ada di Surabaya yaitu ITS (Institut Teknologi Sepuluh Nopember). Melalui komunitas satelitnya yaitu ITS-SAT, mahasiswa dari berbagai jurusan yang memiliki minat di bidang satelit dibimbing dan diikutkan dalam pengembangan penelitian satelit. Saat ini yang sedang dalam penelitian adalah sistem komunikasi dari satelit nano ke stasiun bumi untuk pengiriman informasi berupa citra dengan frekuensi operasi sebesar 2,4 GHz.

Pada sistem komunikasi dari satelit ke stasiun bumi, terdapat beberapa blok penyusun agar sistem dapat beroperasi dengan baik, dan salah satunya adalah blok pengkodean kanal di sisi satelit. Dalam makalah ini, dilakukan perancangan sistem pengkodean kanal menggunakan *Reed Solomon* (255,239) yang diimplementasikan ke dalam perangkat keras FPGA (Field Programmable Gate Array) Cyclone II dengan

menggunakan bahasa pemrograman VHDL (VHSIC (Very High Speed Integrated Circuit) Hardware Description Language). Penggunaan perangkat keras FPGA didasarkan pada kemampuannya untuk dapat mentransfer data dengan kecepatan tinggi sehingga cocok untuk data berupa citra yang memiliki kapasitas besar, dan dapat beroperasi pada frekuensi yang semakin tinggi, sehingga menjadi fungsi penting pada sistem di satelit. Metode pengkodean kanal Reed Solomon adalah mekanisme menambah simbol parity (codeword) ke dalam data saat proses pengiriman dengan tujuan meningkatkan kemampuan koreksi kesalahan data yang akan diterima. Kode Reed Solomon direpresentasikan dengan format RS (n,k) dimana n adalah panjang keseluruhan informasi yang telah dikodekan, sedangkan k adalah panjang informasi awal [1].

Dalam makalah ini memuat sistematika penulisan yang terdiri atas bagian pendahuluan yang berisi latar belakang dari judul makalah, dan deskripsi singkat dari penelitian yang dilakukan. Bagian teori penunjang berisi pembahasan beberapa teori yang menunjang penelitian. Bagian perancangan sistem membahas metode — metode yang dilakukan untuk merancang suatu sistem sehingga tujuan dari penelitian dapat tercapai. Bagian hasil dan pembahasan berisi tentang hasil data yang diperoleh baik dari simulasi maupun implementasi, serta pembahasan dari data yang diperoleh. Bagian kesimpulan/ringkasan menyimpulkan seluruh kegiatan maupun hasil yang diperoleh dari penelitian yang dilakukan.

Makalah ini membahas mengenai pengkodean kanal *Reed Solomon* yang berbasis *FPGA* untuk transmisi citra pada satelit nano. Sedangkan untuk pendekodean kanal *Reed Solomon* dibahas pada makalah lain [2].

# II. TEORI PENUNJANG

# A. Pengkodean Kanal Reed Solomon

Sebuah kode *Reed Solomon* ditulis dalam bentuk RS(n,k) dimana n adalah panjang blok atau panjang kode yang terdiri dari susunan beberapa simbol, sedangkan k adalah panjang informasi atau jumlah simbol data yang akan dikodekan. Panjang *block code* ini adalah  $n = 2^m-1$ , dimana m adalah jumlah bit per simbol. Jumlah simbol *parity* yang harus ditambahkan untuk mengkoreksi sejumlah *error* t adalah n-k=2t.

Panjang blok (n)

Gambar. 1. Elemen kode Reed Solomon. [1]

# Elemen Galois Field

Elemen *galois field* terdiri dari sekumpulan elemen yang dinotasikan oleh  $\alpha$ , dan bernilai :

$$0, \alpha^0, \alpha^1, \alpha^2, ..., \alpha^{n-1}$$

(1)

untuk membentuk sebuah set dari elemen  $2^m$ , dimana  $n = 2^{m-1}$ . Nilai dari  $\alpha$  biasanya dipilih bernilai 2, meskipun nilai lain dapat digunakan. Tiap elemen *field* yang ditunjukkan pada persamaan (1) dapat direpresentasikan dalam bentuk polinomial:

$$\alpha^{m-1}x^{m-1} + \dots + \alpha^1x + \alpha^0 \tag{2}$$

Untuk *m*=4 memiliki persamaan elemen *Galois Field* berikut :

$$\alpha^3 x^3 + \alpha^2 x^2 + \alpha^1 \alpha^1 + \alpha^0$$

Aritmatik dalam elemen *galois field* memiliki proses penjumlahan, pengurangan, perkalian, dan pembagian yang bebeda dengan operasi pada bilangan integer.

$$13 + 3 = 1101 \text{ XOR } 0011 = 1110 = 14.$$

$$13 \times 3 = \alpha^{13} \times \alpha^4 = \alpha^{17 \mod 15} = \alpha^2 = 4$$

$$13/3 = a^{13}/a^4 = a^9 = 10$$

## Polynomial Generator Field

Polinomial generator *field* sering juga disebut polinomial primitif, p(x), dengan pangkat m. Untuk *galois field* dengan ukuran tertentu, memiliki bentuk polinomial yang secara umum sudah sering digunakan, lihat Tabel 1.

## Pembentukan Galois Field (GF)

Pada Tabel 2 menunjukkan nilai dari elemen *field* untuk  $GF(2^m)$  dalam bentuk indeks, polinomial, biner, dan desimal. Berdasarkan Tabel 2, tiap tahap pembentukan polinomial selalu dikalikan dengan 'x', sedangkan untuk pembentukan bilangan biner mewakili nilai-nilai koefisien polinomial.

#### Pembentukan Polynomial Generator Code

Bentuk umum dari persamaan polynomial generator code adalah:

$$g(x) = (x + a^b)(x + a^{b+1}) \dots (x + a^{b+2t-1})$$

(3)

Untuk RS(15,11) maka polynomial generator codenya:

$$g(x) = (x + a^0)(x + a^1)(x + a^2)(x + a^3)$$

=  $(x^4 + 15x^3 + 3x^2 + x + 12)$

# Proses Pengkodean Reed Solomon

Contoh *encoding* sederhana akan ditunjukkan pada *encoding* RS (15,11) berikut. Misalkan terdapat 11 *byte* data yang akan dikodekan dengan menggunakan RS (15,11). Data tersebut setelah diubah dalam bentuk desimal menjadi 1,2,3,4,5,6,7,8,9,10,11. Data tersebut direpresentasikan dalam bentuk polinomial menjadi:

Tabel 1. Bentuk polinomial primitif dari nilai m tertentu[1]

| m  |                              | m  | 1                                  |

|----|------------------------------|----|------------------------------------|

| 3  | $1 + X + X^3$                | 14 | 4 $1+X+X^6+X^{10}+X^{14}$          |

| 4  | $1 + X + X^4$                | 15 | $5  1 + X + X^{15}$                |

| 5  | $1 + X^2 + X^5$              | 16 | $6  1 + X + X^{3+}X^{12} + X^{16}$ |

| 6  | $1 + X + X^6$                | 17 | $7  1 + X^3 + X^{17}$              |

| 7  | $1 + X^3 + X^7$              | 18 | ·                                  |

| 8  | $1 + X^2 + X^3 + X^4 + X^8$  | 19 | $9  1 + X + X^{2+}X^5 + X^{19}$    |

| 9  | $1 + X^4 + X^9$              | 20 | $0  1 + X^3 + X^{20}$              |

| 10 | $1 + X^3 + X^{10}$           | 21 | $1 + X^2 + X^{21}$                 |

| 11 | $1 + X^2 + X^{11}$           | 22 | $2   1 + X + X^{22}$               |

| 12 | $1 + X + X^4 + X^6 + X^{12}$ | 23 | -                                  |

| 13 | $1 + X + X^3 + X^4 + X^{13}$ | 24 | $4  1 + X + X^{2+}X^{7} + X^{24}$  |

Tabel 2.

Nilai elemen - elemen field untuk GF(16) [3] Bentuk Bentuk polinomial Bentuk Bentuk index biner desimal 0 0000 0 0  $\alpha^0$ 1 0001 1  $x^1$ 2  $\alpha^{1}$ 0010  $\alpha^2$  $x^2$ 0100 4  $\alpha^3$  $x^3$ 1000 8  $\alpha^4$  $x^1 + 1$ 0011 3  $\alpha^5$  $x^2 + x$ 0110 6  $\alpha^{6}$  $x^3 + x^2$ 1100 12  $x^3 + x + 1$ 1011 11  $\alpha$  $x^2 + 1$  $\alpha^8$ 0101 5  $\alpha^{9}$  $x^3 + x$ 1010 10  $\alpha^{\overline{10}}$  $x^2 + x + 1$ 0111 7  $x^3 + x^2 + x$ 1110 14  $\alpha^{\,\overline{12}}$  $x^3 + x^2 + x + 1$ 1111 15  $\alpha^{\overline{13}}$  $x^3 + x^2 + 1$ 1101 13  $\alpha^{14}$  $x^3 + 1$ 1001 9

$$x^{10} + 2x^9 + 3x^8 + 4x^7 + 5x^6 + 6x^5 + 7x^4 + 8x^3 + 9x^2 + 10x + 11$$

Data polinomial ini kemudian dikalikan dengan  $x^{2e}$ , dimana 2e = 4 sehingga data polinomial dikalikan dengan  $x^4$ . Hal ini dilakukan untuk menyediakan tempat bagi *codeword* yang akan diletakkan di belakang data. Hasil perkaliannya adalah :

$$x^{14} + 2x^{13} + 3x^{12} + 4x^{11} + 5x^{10} + 6x^9 + 7x^8 + 8x^7 + 9x^6 + 10x^5 + 11x^4$$

Polinomial ini kemudian dibagi dengan polinomial dari kode generator yaitu  $g(x) = x^4 + 15x^3 + 3x^2 + x + 12$

sehingga menghasilkan 4 codeword [3].

```

x^{14} x^{13} x^{12} x^{11} x^{10} x^{9} x^{8} x^{7} x^{6} x^{5} x^{4} x^{3} x^{2} x^{1} x^{0}

0 0 0

1

15 3 1 12

15

3

1 12

2

13

7

4

13

4

5

3

11

7

14

8

4

4

10

12

13 10

4

9

8

<u>5</u>

15 13 1 12

6 11

0

6

0___

0

0

11

0

12

7

12

8 7

12 15

8 11 12 15

8

0

0

0

11

12

15 0

9

13

2

6

11

9

2 11

10

3 14 11 13

12 0 13

10

11

15 3 1 12

3 3 12 12

```

Di bagian akhir diperoleh 4 simbol yaitu 3, 3, 12, 12, inilah yang disebut dengan *codeword* yang nantinya ditempatkan di belakang data yang dikodekan, yaitu menjadi 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 3, 3, 12, 12.

## B. Pengenalan Citra

Citra adalah suatu representasi, kemiripan, atau imitasi dari suatu objek atau benda. Citra yang terlihat merupakan cahaya yang direfleksikan dari sebuah objek. Sumber cahaya menerangi objek, objek memantulkan kembali sebagian dari berkas cahaya tersebut dan pantulan cahaya ditangkap oleh alat-alat optik, misalnya mata manusia, kamera, *scanner*, sensor satelit, dan sebagainya, kemudian direkam [4]. Citra sebagai keluaran dari suatu sistem perekaman data dapat

bersifat optik, analog, ataupun digital. Beberapa jenis citra digital yang sering digunakan adalah citra biner, citra grayscale, dan citra warna. Salah satu tipe format citra warna digital adalah format *JPEG* dimana merupakan format gambar yang telah mengalami kompresi semaksimal mungkin (kompresi *lossy*) untuk kepentingan *sharing* dan *preview* dengan ukuran *file* yang sangat kecil. Setiap piksel pada *file JPEG* memiliki tiga nilai untuk masing – masing warna digital (RGB), dan tiap warna memiliki kedalaman 8 bit, oleh karena itu kedalaman tiap piksel adalah 24 bit tiap piksel.

# C. FPGA (Field Programmable Logic Array)

FPGA adalah IC digital yang berisi sekumpulan blok logika yang dapat dikonfigurasi [5]. Proses pemrograman pada FPGA terbagi kedalam beberapa tahap yaitu tahap awal berupa design entry, functional simulation, synthesis, implementation, timing simulation, dan device programming.

# D. VHDL (VHSIC Hardware Description Language)

VHDL adalah bahasa pemrograman yang digunakan dalam membuat perancangan program. Deskripsi *VHDL* terdiri dari unit desain primer dan sekunder. Unit desain primer adalah *entity* dan *architecture*, sedangkan unit desain sekunder adalah *package* dan *package body*. Unit desain sekunder selalu berhubungan dengan unit desain utama. Kumpulan dari unit desain ini disimpan di dalam *library* [6].

#### III. PERANCANGAN SISTEM

#### A. Analisa Kebutuhan

Untuk membuat program aplikasi dibutuhkan komponen pendukung dari sisi perangkat keras (*hardware*) berupa modul FPGA, laptop, beberapa jenis kabel sebagai pendukung antarmuka antara perangkat seperti kabel serial RS-232 dan kabel paralel *ribbon*. Selain perangkat keras juga terdapat perangkat lunak berupa *software Quartus II* yang mendukung bahasa pemrograman *VHDL*.

## B. Rancangan Sistem

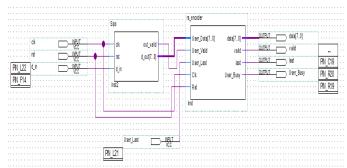

Rancangan sistem yang akan dibuat dapat dilihat pada blok diagram seperti tampak pada Gambar 2. Berdasarkan blok diagram pada Gambar 2, terdapat blok PC (Transmitter) yang berfungsi untuk mengirimkan informasi berupa data citra dan data teks melalui port serial komputer (USB) menuju ke port RS-232 FPGA. Karena menggunakan komunikasi secara serial maka data yang keluar dari PC adalah data serial. Selain itu juga terdapat blok FPGA (Encoder) yang berfungsi untuk mengkodekan informasi yang diterima dari *PC* (*Transmitter*). Oleh karena itu blok ini berisi program encoder Reed Solomon (255,239) dengan menggunakan bahasa VHDL. Selain program encoder, di dalamnya juga terdapat program konversi dari serial to parallel. Hal ini disebabkan karena data yang diterima dari komputer berupa serial sedangkan inputan data untuk *encoder* adalah parallel (8 bit), sehingga perlu program pengubah data dari serial ke parallel. Setelah informasi dikodekan maka data dikeluarkan dalam format parallel 8 bit melalui port GPIO (General Purpose Input Output), menuju ke port GPIO dari perangkat FPGA yang kedua. Dalam perangkat ini berisi program konversi dari paralel ke serial, sehingga output dari encoder dapat diamati di PC (Receiver).

## JURNAL TEKNIK POMITS Vol. 2, No. 1, (2013) ISSN: 2337-3539 (2301-9271 Print)

FPGA (Piso)

PC (Transmitter

PC (Receiver)

Gambar. 2. Diagram blok sistem

Gambar. 3. Diagram skematik encoder

Gambar. 4. Hasil encoder RS (255,239)

Perancangan Sistem Encoder RS (255,239)

Dalam perancangan ini selain program encoder juga terdapat program sipo. Pada gambar 3 menunjukkan diagram skematik sistem *encoder* RS(255,239).

Di dalam diagram skematik *encoder* terdapat susunan program *Reed Solomon encoder* dengan bahasa *VHDL* yang diantaranya terdiri atas program pembentukan paket *encoder*, dan pembentukan elemen dan nilai elemen *galois field*. Selain itu juga terdapat program *serial in paralel out*.

Perancangan Sistem Pengujian Interface RS-232 (UART)

Perancangan sistem ini dimaksudkan untuk mengetahui apakah *port* serial RS-232 dapat langsung beroperasi tanpa adanya program *UART* atau perlu membuat program tersebut. Untuk mengetahui hal tersebut maka dibuatlah sistem *loopback*. Sistem *loopback* dibentuk dengan menggunakan dua buah gerbang NOT yang saling terhubung, sehingga dapat berfungsi sebagai *jumper* antara *RX* dengan *TX* pada *port* serial RS-232.

Perancangan Sistem Pengujian Komunikasi Dua Buah FPGA

Setelah diketahui bahwa komunikasi serial RS-232 telah berhasil, maka dilakukan pengujian komunikasi antara dua buah FPGA menggunakan interface GPIO. Dalam pengujian ini digunakan program sipo (serial in paralel out) dan piso (paralel in serial out), dimana program sipo diterapkan pada FPGA 1 sedangkan program piso untuk FPGA 2, dan antar FPGA dihubungkan dengan kabel ribbon pada port GPIO dari masing – masing FPGA.

Perancangan Sistem Pengujian Encoder dan Decoder Pada Dua Buah FPGA

Setelah diketahui bahwa pengujian komunikasi antara dua buah FPGA dengan menggunakan program sipo dan piso berhasil maka selanjutnya untuk tahap terakhir adalah menyisipkan program encoder setelah program sipo pada perangkat FPGA (Encoder). Proses pengujian program encoder ini dilakukan dengan mengirimkan informasi berupa citra dalam format JPEG dari PC (Transmitter) kemudian diterima oleh PC (Receiver). Untuk data hasil encoder berupa penambahan codeword tidak dapat diamati diimplementasikan ke *hardware* namun hanya dapat diamati melalui simulasi pada ModelSim Altera Simulator. Dalam menjalankan fungsi dari sistem encoder, dilakukan beberapa pengaturan di tiap – tiap bloknya agar terbentuk kesesuaian antarsistem yaitu pengaturan pin planner pada FPGA dan pengaturan baud rate pada console terminal emulator.

## IV. HASIL DAN PEMBAHASAN

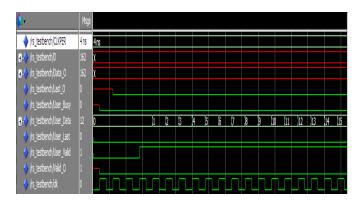

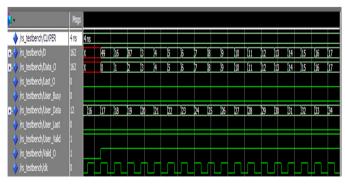

# A. Hasil Simulasi Pengkodean Reed Solomon (255,239)

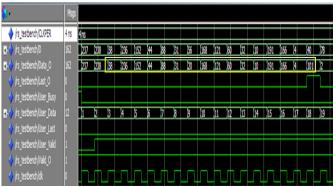

Simulasi program *encoding Reed Solomon* dilakukan melalui *ModelSim Altera simulator* dan hasilnya tampak pada Gambar 4. Berdasarkan Gambar 4, saat data *input encoder* mulai terhitung dari 0 hingga 238 *byte* (239 *byte*) maka terjadi penambahan *codeword* sebanyak 16 *byte* dibelakang simbol informasi, seperti yang terlihat pada Tabel 3.

## JURNAL TEKNIK POMITS Vol. 2, No. 1, (2013) ISSN: 2337-3539 (2301-9271 Print)

Table 3. Nilai *Codeword* Untuk Simbol Informasi 0-238 *Byte*

| Simbol<br>informasi<br>(Data input) | 0 hingga 238 byte                                        |  |  |  |  |  |  |  |  |  |

|-------------------------------------|----------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Codeword                            | 58 236 152 44 88 31 20 168 121 60 32<br>10 191 166 4 101 |  |  |  |  |  |  |  |  |  |

Gambar. 5. Citra yang akan dikodekan

Gambar. 6 Bagian kecil dari citra yang akan dikodekan

| <b>≝</b> Ar | ≨ Array Editor - citra |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|-------------|------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|             | ½ № 6   ∰              |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| 164         | 164                    | 166 | 166 | 166 | 166 | 167 | 168 | 168 | 169 | 170 | 171 | 171 | 172 | 172 | 172 | 173 | 174 | 174 | 175 | 175 | 175 | 176 | 176 | 176 |

| 164         | 165                    | 165 | 166 | 166 | 167 | 167 | 168 | 168 | 169 | 170 | 171 | 172 | 172 | 172 | 172 | 173 | 174 | 174 | 176 | 176 | 176 | 176 | 176 | 177 |

| 166         | 165                    | 166 | 167 | 168 | 168 | 168 | 169 | 169 | 170 | 171 | 172 | 172 | 173 | 173 | 173 | 174 | 175 | 175 | 176 | 176 | 176 | 176 | 176 | 177 |

| 167         | 167                    | 167 | 168 | 169 | 169 | 169 | 170 | 170 | 171 | 172 | 172 | 173 | 174 | 174 | 174 | 175 | 176 | 176 | 177 | 177 | 178 | 178 | 178 | 178 |

| 166         | 168                    | 168 | 169 | 168 | 169 | 169 | 170 | 171 | 171 | 173 | 173 | 174 | 174 | 175 | 175 | 176 | 176 | 177 | 176 | 177 | 178 | 179 | 180 | 180 |

| 168         | 168                    | 169 | 170 | 170 | 171 | 171 | 172 | 172 | 172 | 174 | 174 | 175 | 175 | 175 | 175 | 176 | 177 | 177 | 178 | 178 | 178 | 179 | 180 | 180 |

| 169         | 169                    | 170 | 170 | 171 | 171 | 172 | 173 | 173 | 174 | 174 | 175 | 175 | 176 | 177 | 177 | 177 | 178 | 179 | 178 | 179 | 179 | 180 | 181 | 183 |

| 170         | 170                    | 171 | 171 | 172 | 172 | 173 | 174 | 174 | 175 | 176 | 176 | 176 | 177 | 177 | 177 | 178 | 179 | 179 | 180 | 180 | 181 | 182 | 183 | 182 |

| 170         | 171                    | 172 | 172 | 172 | 174 | 174 | 175 | 175 | 175 | 176 | 176 | 177 | 178 | 178 | 178 | 178 | 179 | 180 | 181 | 182 | 182 | 183 | 183 | 183 |

| 171         | 171                    | 172 | 173 | 173 | 174 | 175 | 175 | 175 | 176 | 177 | 177 | 177 | 178 |     |     |     |     |     |     |     |     |     |     |     |

Gambar. 7. Deretan simbol informasi citra sebelum dikodekan sebanyak 239 byte

| Edito   | or - C\MATLAB701\work\encode.m                            | _       |

|---------|-----------------------------------------------------------|---------|

| File Ed | lit Text Cell Tools Debug Desktop Window Help             | X 5   E |

| <u></u> |                                                           |         |

| 1 -     | m = 8;                                                    |         |

| 2 -     | $n = 2^m-1;$                                              |         |

| 3 -     | k = 239;                                                  |         |

| 4 -     | msg = gf ([ 164 164 166 166 166 166 167 168 168 169 170 1 | 71 171  |

| 5 -     | code = rsenc (msg,n,k)                                    |         |

Gambar. 8. Simulasi RS encoder dengan Matlab

# B. Simulasi Pengkodean Reed Solomon Pada Citra

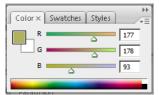

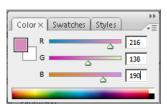

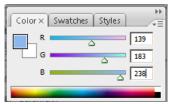

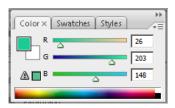

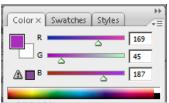

Berdasarkan data hasil pengkodean diperoleh sejumlah simbol tambahan dimana deretan simbol tambahan ini ada yang menyisip diantara deretan data 3 *byte* untuk 1 *pixel* yaitu pada simbol 93, dan ketika dicek pada tool *navigator color photoshop* menghasilkan warna yang berbeda.

| Command Wi | ndow    |        |     |     |     |     | 7   |

|------------|---------|--------|-----|-----|-----|-----|-----|

| Columns    | 209 thr | ough 2 | 16  |     |     |     |     |

| 175        | 175     | 176    | 176 | 177 | 178 | 178 | 178 |

| Columns    | 217 thr | ough 2 | 24  |     |     |     |     |

| 178        | 179     | 180    | 181 | 182 | 182 | 183 | 183 |

| Columns    | 225 thr | ough 2 | 32  |     |     |     |     |

| 183        | 171     | 171    | 172 | 173 | 173 | 174 | 175 |

| Columns    | 233 thr | ough 2 | 40  |     |     |     |     |

| 175        | 175     | 176    | 177 | 177 | 177 | 178 | 93  |

| Columns    | 241 thr | ough 2 | 48  |     |     |     |     |

| 216        | 138     | 190    | 139 | 183 | 238 | 26  | 203 |

| Columns    | 249 thr | ough 2 | 55  |     |     |     |     |

| 148        | 169     | 45     | 187 | 180 | 73  | 125 |     |

Gambar. 9. Deretan simbol informasi citra setelah dikodekan sebanyak 255 byte

Gambar. 10. Hasil warna untuk deretan simbol 177,178,93

Gambar. 11. Hasil warna untuk deretan simbol 216,138,190

Gambar. 12. Hasil warna untuk deretan simbol 139,183,238

Gambar .13. Hasil warna untuk deretan simbol 26,203,148

Gambar . 14. Hasil Warna Untuk Deretan Simbol 169,45,187

Gambar. 15. Hasil warna untuk deretan simbol 180,73,125

Gambar. 16. Citra inputan encoder

Gambar. 17. Output citra encoder

Berdasarkan hasil data yang diperoleh, warna lain yang terbentuk akibat adanya deretan simbol *parity* setelah deretan simbol informasi sebanyak 239 *byte*, banyak menghasilkan warna merah jambu (*pink*) dan juga warna hijau agak kebiru – biruan.

C. Hasil Implementasi Program Encoder Pada Perangkat FPGA Untuk Pengiriman Citra.

Saat dilakukan implementasi program encoder pada perangkat FPGA, informasi yang dikirim berupa data citra dengan format JPEG. Pengiriman informasi dengan kapasitas yang berbeda – beda dilakukan pada baud rate sebesar 9600 bps. Untuk citra pada Gambar 16 merupakan citra sebelum dikodekan dan Gambar 17 merupakan citra hasil pengkodean. File citra yang dikirim melalui console terminal emulator memiliki kapasitas sebesar 68,1 KB. Berdasarkan citra hasil pengkodean terlihat bahwa citra tidak sesuai dengan file aslinya hal ini disebabkan karena telah terjadi penambahan codeword pada deretan simbol citra tersebut. Karena tiap deretan simbol tertentu mewakili warna tertentu maka ketika susunan simbol tersebut berubah maka warna yang dihasilkan juga ikut berubah. Seperti yang terlihat di Gambar 4.16 yang menghasilkan dominan warna merah jambu (pink), kemudian terdapat juga warna hijau kebiru – biruan pada bagian wajah dan juga terdapat warna kuning. Warna — warna yang dihasilkan saat implementasi hampir sama dengan yang dihasilkan dari simulasi, namun karena saat simulasi hanya mengambil sebagian kecil dari data informasi yaitu sebanyak 239 *byte* maka tidak terlalu jelas perbedaan warna yang dapat dilihat antara implementasi dan simulasi.

#### V. KESIMPULAN/RINGKASAN

Nilai codeword yang terbentuk pada encoder RS (255,239) pada simulasi ModelSim Altera untuk simbol informasi dari 0 hingga 238 byte adalah 58 236 152 44 88 31 20 168 121 60 32 10 191 166 4 101. Nilai codeword yang terbentuk pada encoder RS (255,239) pada simulasi Matlab untuk deretan simbol informasi citra adalah 93 216 138 190 139 183 238 26 203 148 169 45 187 180 73 125. Deretan simbol 177,178,93 menghasilkan warna kuning gelap, deretan simbol 216,138,190 menghasilkan warna merah muda (pink), deretan simbol 139,183,238 menghasilkan warna biru muda, deretan simbol 26,203,148 menghasilkan warna hijau kebiruan, deretan simbol 169,45,187 menghasilkan warna nila, dan deretan simbol 180,73,125 menghasilkan warna merah muda (pink). Antara hasil simulasi matlab dan implementasi menghasilkan perubahan warna yang hampir sama yaitu dominan warna merah muda (pink). Faktor yang menyebabkan terjadinya perubahan warna pada citra setelah dikodekan vaitu karena adanya penambahan *codeword* pada data citra asli.

#### UCAPAN TERIMA KASIH

Penulis mengucapkan terima kasih kepada tim penelitian strategis nasional 2012 Kemdikbud "Pengembangan stasiun bumi untuk komunikasi data, citra, dan video dengan satelit LEO VHF/UHF/S-band menuju kemandirian teknologi satelit" yang telah memberikan dukungan finansial.

#### DAFTAR PUSTAKA

- Sklar, Bernard, "Digital Communications", Prentice Hall, Upper Saddle River, New Jersey, 2001.

- [2] Utami, Andi Nurul, "Pendekodean Reed Solomon Berbasis FPGA Untuk Transmisi Citra Pada Sistem Komunikasi Satelit Nano", Laporan Tugas Akhir Jurusan Teknik Elektro ITS, Surabaya, Januari, 2013.

- [3] Clarke, C.K.P., "Reed-Solomon Error Correction", White Paper Research & Development British Broadcasting Corporation (R & D BBC), United Kingdom, Juli, 2002.

- [4] Li, Ze-Nian dan Mark S. Drew, "Fundamentals of Multimedia", Prentice Hall, Upper Saddle River, New Jersey, 2004.

- [5] Meyer-Baese, Uwe, "Digital Signal Processing With Field Programmable Gate Arrays", Springer, Verlag Berlin Heidelberg, 2001.

- [6] Perry, Douglas L., "VHDL Programming by Example", United States of America, Edisi Keempat, 1976.